### Spartan-3E FPGA Family Data Sheet

© Copyright 2005–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

www.xilinx.com

#### DS312 December 14, 2018

### Module 1: Introduction and Ordering Information

### DS312 (v4.2) December 14, 2018

- Introduction

- Features

- Architectural Overview

- Package Marking

- Ordering Information

#### Module 2: Functional Description

### DS312 (v4.2) December 14, 2018

- Input/Output Blocks (IOBs)

- Overview

- SelectIO<sup>™</sup> Signal Standards

- Configurable Logic Block (CLB)

- Block RAM

- Dedicated Multipliers

- Digital Clock Manager (DCM)

- Clock Network

- Configuration

- Powering Spartan®-3E FPGAs

- Production Stepping

#### Module 3: DC and Switching Characteristics DS312 (v4.2) December 14, 2018

- DC Electrical Characteristics

- Absolute Maximum Ratings

- Supply Voltage Specifications

- Recommended Operating Conditions

- DC Characteristics

- Switching Characteristics

- I/O Timing

- SLICE Timing

- DCM Timing

- Block RAM Timing

- Multiplier Timing

- Configuration and JTAG Timing

#### Module 4: Pinout Descriptions

#### DS312 (v4.2) December 14, 2018

- Pin Descriptions

- Package Overview

- Pinout Tables

- Footprint Diagrams

Send Feedback

## Product Specification

#

### Spartan-3E FPGA Family: Introduction and Ordering Information

DS312 (v4.2) December 14, 2018

#### **Product Specification**

### Introduction

The Spartan®-3E family of Field-Programmable Gate Arrays (FPGAs) is specifically designed to meet the needs of high volume, cost-sensitive consumer electronic applications. The five-member family offers densities ranging from 100,000 to 1.6 million system gates, as shown in Table 1.

The Spartan-3E family builds on the success of the earlier Spartan-3 family by increasing the amount of logic per I/O, significantly reducing the cost per logic cell. New features improve system performance and reduce the cost of configuration. These Spartan-3E FPGA enhancements, combined with advanced 90 nm process technology, deliver more functionality and bandwidth per dollar than was previously possible, setting new standards in the programmable logic industry.

Because of their exceptionally low cost, Spartan-3E FPGAs are ideally suited to a wide range of consumer electronics applications, including broadband access, home networking, display/projection, and digital television equipment.

The Spartan-3E family is a superior alternative to mask programmed ASICs. FPGAs avoid the high initial cost, the lengthy development cycles, and the inherent inflexibility of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary, an impossibility with ASICs.

### Features

- Very low cost, high-performance logic solution for high-volume, consumer-oriented applications

- Proven advanced 90-nanometer process technology

- Multi-voltage, multi-standard SelectIO<sup>™</sup> interface pins

- Up to 376 I/O pins or 156 differential signal pairs

#### Table 1: Summary of Spartan-3E FPGA Attributes

- LVCMOS, LVTTL, HSTL, and SSTL single-ended signal standards

- 3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

- 622+ Mb/s data transfer rate per I/O

- True LVDS, RSDS, mini-LVDS, differential HSTL/SSTL differential I/O

- Enhanced Double Data Rate (DDR) support

- DDR SDRAM support up to 333 Mb/s

- Abundant, flexible logic resources

- Densities up to 33,192 logic cells, including optional shift register or distributed RAM support

- Efficient wide multiplexers, wide logic

- Fast look-ahead carry logic

- Enhanced 18 x 18 multipliers with optional pipeline

- IEEE 1149.1/1532 JTAG programming/debug port

- Hierarchical SelectRAM™ memory architecture

- Up to 648 Kbits of fast block RAM

- Up to 231 Kbits of efficient distributed RAM

- Up to eight Digital Clock Managers (DCMs)

- Clock skew elimination (delay locked loop)

- Frequency synthesis, multiplication, division

- High-resolution phase shifting

- Wide frequency range (5 MHz to over 300 MHz)

- Eight global clocks plus eight additional clocks per each half of device, plus abundant low-skew routing

- Configuration interface to industry-standard PROMs

- Low-cost, space-saving SPI serial Flash PROM

- x8 or x8/x16 parallel NOR Flash PROM

- Low-cost Xilinx® Platform Flash with JTAG

- Complete Xilinx ISE® and WebPACK™ software

- MicroBlaze<sup>™</sup> and PicoBlaze<sup>™</sup> embedded processor cores

- Fully compliant 32-/64-bit 33 MHz <u>PCI support</u> (66 MHz in some devices)

- Low-cost QFP and BGA packaging options

- Common footprints support easy density migration

- Pb-free packaging options

- XA Automotive version available

| Device    | System | Equivalent<br>Logic Cells | CLB Array<br>(One CLB = Four Slices) |         |               |                 | Distributed             | Block<br>RAM        | Dedicated   | DCMs | Maximum  | Maximum<br>Differential |

|-----------|--------|---------------------------|--------------------------------------|---------|---------------|-----------------|-------------------------|---------------------|-------------|------|----------|-------------------------|

| Device    | Gates  |                           | Rows                                 | Columns | Total<br>CLBs | Total<br>Slices | RAM bits <sup>(1)</sup> | bits <sup>(1)</sup> | Multipliers | DCMS | User I/O | I/O Pairs               |

| XC3S100E  | 100K   | 2,160                     | 22                                   | 16      | 240           | 960             | 15K                     | 72K                 | 4           | 2    | 108      | 40                      |

| XC3S250E  | 250K   | 5,508                     | 34                                   | 26      | 612           | 2,448           | 38K                     | 216K                | 12          | 4    | 172      | 68                      |

| XC3S500E  | 500K   | 10,476                    | 46                                   | 34      | 1,164         | 4,656           | 73K                     | 360K                | 20          | 4    | 232      | 92                      |

| XC3S1200E | 1200K  | 19,512                    | 60                                   | 46      | 2,168         | 8,672           | 136K                    | 504K                | 28          | 8    | 304      | 124                     |

| XC3S1600E | 1600K  | 33,192                    | 76                                   | 58      | 3,688         | 14,752          | 231K                    | 648K                | 36          | 8    | 376      | 156                     |

Notes:

1. By convention, one Kb is equivalent to 1,024 bits.

© Copyright 2005–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

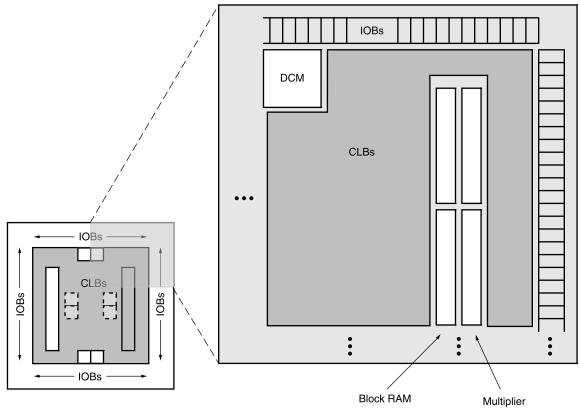

### **Architectural Overview**

The Spartan-3E family architecture consists of five fundamental programmable functional elements:

- Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

- **Block RAM** provides data storage in the form of 18-Kbit dual-port blocks.

- **Multiplier Blocks** accept two 18-bit binary numbers as inputs and calculate the product.

• **Digital Clock Manager (DCM) Blocks** provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XC3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XC3S100E has only one DCM at the top and bottom, while the XC3S1200E and XC3S1600E add two DCMs in the middle of the left and right sides.

The Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

DS312\_01\_111904

Figure 1: Spartan-3E Family Architecture

### Configuration

Spartan-3E FPGAs are programmed by loading configuration data into robust, reprogrammable, static CMOS configuration latches (CCLs) that collectively control all functional elements and routing resources. The FPGA's configuration data is stored externally in a PROM or some other non-volatile medium, either on or off the board. After applying power, the configuration data is written to the FPGA using any of seven different modes:

- Master Serial from a Xilinx Platform Flash PROM

- Serial Peripheral Interface (SPI) from an industry-standard SPI serial Flash

- Byte Peripheral Interface (BPI) Up or Down from an industry-standard x8 or x8/x16 parallel NOR Flash

- Slave Serial, typically downloaded from a processor

- Slave Parallel, typically downloaded from a processor

- Boundary Scan (JTAG), typically downloaded from a processor or system tester.

Furthermore, Spartan-3E FPGAs support MultiBoot configuration, allowing two or more FPGA configuration bitstreams to be stored in a single parallel NOR Flash. The FPGA application controls which configuration to load next and when to load it.

### I/O Capabilities

The Spartan-3E FPGA SelectIO interface supports many popular single-ended and differential standards. Table 2 shows the number of user I/Os as well as the number of differential I/O pairs available for each device/package combination.

Spartan-3E FPGAs support the following single-ended standards:

- 3.3V low-voltage TTL (LVTTL)

- Low-voltage CMOS (LVCMOS) at 3.3V, 2.5V, 1.8V, 1.5V, or 1.2V

- 3V PCI at 33 MHz, and in some devices, 66 MHz

- HSTL I and III at 1.8V, commonly used in memory applications

- SSTL I at 1.8V and 2.5V, commonly used for memory applications

Spartan-3E FPGAs support the following differential standards:

- LVDS

- Bus LVDS

- mini-LVDS

- RSDS

- Differential HSTL (1.8V, Types I and III)

- Differential SSTL (2.5V and 1.8V, Type I)

- 2.5V LVPECL inputs

| Package                | 16 x 16                         |                  | VQG100 CPG132     |                  | TQ144<br>TQG144<br>22 x 22 |                  | PQ208<br>PQG208<br>30.5 x 30.5 |                  | FT256<br>FTG256<br>17 x 17 |                  | FG320<br>FGG320<br>19 x 19 |                   | FG400<br>FGG400<br>21 x 21 |                    | FG484<br>FGG484<br>23 x 23 |                    |

|------------------------|---------------------------------|------------------|-------------------|------------------|----------------------------|------------------|--------------------------------|------------------|----------------------------|------------------|----------------------------|-------------------|----------------------------|--------------------|----------------------------|--------------------|

| Footprint<br>Size (mm) |                                 |                  |                   |                  |                            |                  |                                |                  |                            |                  |                            |                   |                            |                    |                            |                    |

| Device                 | User                            | Diff             | User              | Diff             | User                       | Diff             | User                           | Diff             | User                       | Diff             | User                       | Diff              | User                       | Diff               | User                       | Diff               |

| XC3S100E               | <b>66<sup>(2)</sup></b><br>9(7) | <b>30</b><br>(2) | <b>83</b><br>(11) | <b>35</b><br>(2) | <b>108</b><br>(28)         | <b>40</b><br>(4) | -                              | -                | -                          | -                | -                          | -                 | -                          | -                  | -                          | -                  |

| XC3S250E               | <b>66</b><br>(7)                | <b>30</b><br>(2) | <b>92</b><br>(7)  | <b>41</b><br>(2) | <b>108</b><br>(28)         | <b>40</b><br>(4) | <b>158</b><br>(32)             | <b>65</b><br>(5) | <b>172</b><br>(40)         | <b>68</b><br>(8) | -                          | -                 | -                          | -                  | -                          | -                  |

| XC3S500E               | <b>66<sup>(3)</sup></b><br>(7)  | <b>30</b><br>(2) | <b>92</b><br>(7)  | <b>41</b><br>(2) | -                          | -                | <b>158</b><br>(32)             | <b>65</b><br>(5) | <b>190</b><br>(41)         | <b>77</b><br>(8) | <b>232</b><br>(56)         | <b>92</b><br>(12) | -                          | -                  | -                          | -                  |

| XC3S1200E              | -                               | -                | -                 | -                | -                          | -                | -                              | -                | <b>190</b><br>(40)         | <b>77</b><br>(8) | <b>250</b><br>(56)         | <b>99</b><br>(12) | <b>304</b><br>(72)         | <b>124</b><br>(20) | -                          | -                  |

| XC3S1600E              | -                               | -                | -                 | -                | -                          | -                | -                              | -                | -                          | -                | <b>250</b><br>(56)         | <b>99</b><br>(12) | <b>304</b><br>(72)         | <b>124</b><br>(20) | <b>376</b><br>(82)         | <b>156</b><br>(21) |

#### Table 2: Available User I/Os and Differential (Diff) I/O Pairs

#### Notes:

1. All Spartan-3E devices provided in the same package are pin-compatible as further described in Module 4, Pinout Descriptions.

2. The number shown in **bold** indicates the maximum number of I/O and input-only pins. The number shown in (*italics*) indicates the number of input-only pins.

The XC3S500E is available in the VQG100 Pb-free package and not the standard VQ100. The VQG100 and VQ100 pin-outs are identical and general references to the VQ100 will apply to the XC3S500E.

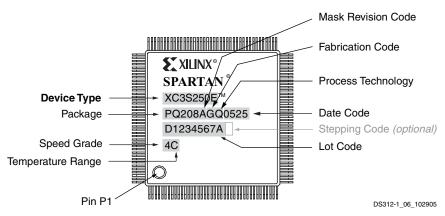

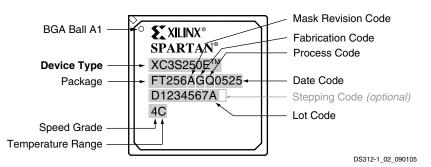

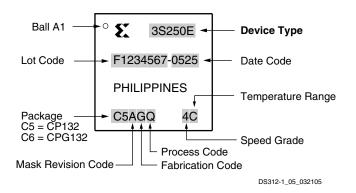

### **Package Marking**

Figure 2 provides a top marking example for Spartan-3E FPGAs in the quad-flat packages. Figure 3 shows the top marking for Spartan-3E FPGAs in BGA packages except the 132-ball chip-scale package (CP132 and CPG132). The markings for the BGA packages are nearly identical to those for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for Spartan-3E FPGAs in the CP132 and CPG132 packages.

On the QFP and BGA packages, the optional numerical Stepping Code follows the Lot Code.

The "5C" and "4I" part combinations can have a dual mark of "5C/4I". Devices with a single mark are only guaranteed for the marked speed grade and temperature range. All "5C" and "4I" part combinations use the Stepping 1 production silicon.

Figure 2: Spartan-3E QFP Package Marking Example

Figure 4: Spartan-3E CP132 and CPG132 Package Marking Example

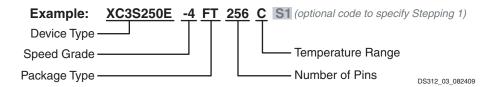

### **Ordering Information**

Spartan-3E FPGAs are available in both standard and Pb-free packaging options for all device/package combinations. All devices are available in Pb-free packages, which adds a 'G' character to the ordering code. All devices are available in either Commercial (C) or Industrial (I) temperature ranges. Both the standard –4 and faster –5 speed grades are available for the Commercial temperature range. However, only the –4 speed grade is available for the Industrial temperature range. See Table 2 for valid device/package combinations.

| Device                  |    | Speed Grade                     |                 | Package Type / Number of Pins                    | Temperature Range (T <sub>J</sub> ) |                             |  |  |

|-------------------------|----|---------------------------------|-----------------|--------------------------------------------------|-------------------------------------|-----------------------------|--|--|

| XC3S100E                | -4 | Standard Performance            | VQ100<br>VQG100 | 100-pin Very Thin Quad Flat Pack (VQFP)          | С                                   | Commercial (0°C to 85°C)    |  |  |

| XC3S250E                | -5 | High Performance <sup>(1)</sup> | CP132<br>CPG132 | 132-ball Chip-Scale Package (CSP)                | I                                   | Industrial (-40°C to 100°C) |  |  |

| XC3S500E <sup>(2)</sup> |    | 1                               | TQ144<br>TQG144 | 144-pin Thin Quad Flat Pack (TQFP)               |                                     |                             |  |  |

| XC3S1200E               |    |                                 | PQ208<br>PQG208 | 208-pin Plastic Quad Flat Pack (PQFP)            |                                     |                             |  |  |

| XC3S1600E               |    |                                 | FT256<br>FTG256 | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |                                     |                             |  |  |

|                         | 1  |                                 | FG320<br>FGG320 | 320-ball Fine-Pitch Ball Grid Array (FBGA)       |                                     |                             |  |  |

|                         |    |                                 | FG400<br>FGG400 | 400-ball Fine-Pitch Ball Grid Array (FBGA)       |                                     |                             |  |  |

|                         |    |                                 | FG484<br>FGG484 | 484-ball Fine-Pitch Ball Grid Array (FBGA)       |                                     |                             |  |  |

#### Notes:

1. The -5 speed grade is exclusively available in the Commercial temperature range.

- 2. The XC3S500E VQG100 is available only in the -4 Speed Grade.

- 3. See DS635 for the XA Automotive Spartan-3E FPGAs.

#### **Production Stepping**

The Spartan-3E FPGA family uses production stepping to indicate improved capabilities or enhanced features.

Stepping 1 is, by definition, a functional superset of Stepping 0. Furthermore, configuration bitstreams generated for any stepping are forward compatible. See Table 72 for additional details.

Xilinx has shipped both Stepping 0 and Stepping 1. Designs operating on the Stepping 0 devices perform similarly on a Stepping 1 device. Stepping 1 devices have been shipping since 2006. The faster speed grade (-5), Industrial (I grade), Automotive devices, and -4C devices with date codes 0901 (2009) and later, are always Stepping 1 devices. Only -4C devices have shipped as Stepping 0 devices.

To specify only the later stepping for the -4C, append an S# suffix to the standard ordering code, where # is the stepping number, as indicated in Table 3.

#### Table 3: Spartan-3E Optional Stepping Level Ordering

| Stepping<br>Number | Suffix Code | Status     |

|--------------------|-------------|------------|

| 0                  | None or S0  | Production |

| 1                  | S1          | Production |

The stepping level is optionally marked on the device using a single number character, as shown in Figure 2, Figure 3, and Figure 4.

### **Revision History**

The following table shows the revision history for this document.

| Date       | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/2005 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                |

| 03/21/2005 | 1.1     | Added XC3S250E in CP132 package to Table 2. Corrected number of differential I/O pairs for CP132 package. Added package markings for QFP packages (Figure 2) and CP132/CPG132 packages (Figure 4).                                                                                                                                                                                                     |

| 11/23/2005 | 2.0     | Added differential HSTL and SSTL I/O standards. Updated Table 2 to indicate number of input-only pins. Added Production Stepping information, including example top marking diagrams.                                                                                                                                                                                                                  |

| 03/22/2006 | 3.0     | Upgraded data sheet status to Preliminary. Added XC3S100E in CP132 package and updated I/O counts for the XC3S1600E in FG320 package (Table 2). Added information about dual markings for – 5C and –4I product combinations to Package Marking.                                                                                                                                                        |

| 11/09/2006 | 3.4     | Added 66 MHz PCI support and links to the Xilinx PCI LogiCORE data sheet. Indicated that Stepping 1 parts are Production status. Promoted Module 1 to Production status. Synchronized all modules to v3.4.                                                                                                                                                                                             |

| 04/18/2008 | 3.7     | Added XC3S500E VQG100 package. Added reference to XA Automotive version. Updated links.                                                                                                                                                                                                                                                                                                                |

| 08/26/2009 | 3.8     | Added paragraph to Configuration indicating the device supports MultiBoot configuration. Added package sizes to Table 2. Described the speed grade and temperature range guarantee for devices having a single mark in paragraph 3 under Package Marking. Deleted Pb-Free Packaging example under Ordering Information. Revised information under Production Stepping. Revised description of Table 3. |

| 10/29/2012 | 4.0     | Added Notice of Disclaimer. This product is not recommended for new designs.<br>Updated Table 2 footprint size of PQ208.                                                                                                                                                                                                                                                                               |

| 07/19/2013 | 4.1     | Removed banner. This product IS recommended for new designs.                                                                                                                                                                                                                                                                                                                                           |

| 12/14/2018 | 4.2     | Updated for Lead-Frame Plating Composition Change For Legacy Eutectic Products (XCN18024).                                                                                                                                                                                                                                                                                                             |

### **Notice of Disclaimer**

THE XILINX HARDWARE FPGA AND CPLD DEVICES REFERRED TO HEREIN ("PRODUCTS") ARE SUBJECT TO THE TERMS AND CONDITIONS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED IN THE XILINX DATA SHEET. ALL SPECIFICATIONS ARE SUBJECT TO CHANGE WITHOUT NOTICE. PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, OR ANY OTHER APPLICATION THAT INVOKES THE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). USE OF PRODUCTS IN CRITICAL APPLICATIONS IS AT THE SOLE RISK OF CUSTOMER, SUBJECT TO APPLICABLE LAWS AND REGULATIONS.

#### CRITICAL APPLICATIONS DISCLAIMER

XILINX PRODUCTS (INCLUDING HARDWARE, SOFTWARE AND/OR IP CORES) ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS IN LIFE-SUPPORT OR SAFETY DEVICES OR SYSTEMS, CLASS III MEDICAL DEVICES, NUCLEAR FACILITIES, APPLICATIONS RELATED TO THE DEPLOYMENT OF AIRBAGS, OR ANY OTHER APPLICATIONS THAT COULD LEAD TO DEATH, PERSONAL INJURY OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (INDIVIDUALLY AND COLLECTIVELY, "CRITICAL APPLICATIONS"). FURTHERMORE, XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN ANY APPLICATIONS THAT AFFECT CONTROL OF A VEHICLE OR AIRCRAFT, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR. CUSTOMER AGREES, PRIOR TO USING OR DISTRIBUTING ANY SYSTEMS THAT INCORPORATE XILINX PRODUCTS, TO THOROUGHLY TEST THE SAME FOR SAFETY PURPOSES. TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN CRITICAL APPLICATIONS.

#### AUTOMOTIVE APPLICATIONS DISCLAIMER

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

### Spartan-3E FPGA Family: Functional Description

DS312 (v4.2) December 14, 2018

#### **Product Specification**

### **Design Documentation Available**

The functionality of the Spartan®-3E FPGA family is now described and updated in the following documents. The topics covered in each guide are listed below.

- <u>UG331</u>: Spartan-3 Generation FPGA User Guide

- Clocking Resources

- Digital Clock Managers (DCMs)

- Block RAM

- Configurable Logic Blocks (CLBs)

- Distributed RAM

- SRL16 Shift Registers

- Carry and Arithmetic Logic

- I/O Resources

- Embedded Multiplier Blocks

- Programmable Interconnect

- ISE® Design Tools

- IP Cores

- Embedded Processing and Control Solutions

- Pin Types and Package Overview

- Package Drawings

- Powering FPGAs

- Power Management

- UG332: Spartan-3 Generation Configuration User Guide

- Configuration Overview

- Configuration Pins and Behavior

- Bitstream Sizes

- Detailed Descriptions by Mode

- Master Serial Mode using Xilinx® Platform Flash PROM

- Master SPI Mode using Commodity SPI Serial Flash PROM

- Master BPI Mode using Commodity Parallel NOR Flash PROM

- Slave Parallel (SelectMAP) using a Processor

- Slave Serial using a Processor

- JTAG Mode

- ISE iMPACT Programming Examples

- MultiBoot Reconfiguration

© Copyright 2005–2018 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Create a Xilinx user account and sign up to receive automatic e-mail notification whenever this data sheet or the associated user guides are updated.

#### Sign Up for Alerts on Xilinx.com

https://secure.xilinx.com/webreg/register.do ?group=myprofile&languageID=1

### Spartan-3E FPGA Starter Kit

For specific hardware examples, please see the Spartan-3E FPGA Starter Kit board web page, which has links to various design examples and the user guide.

- Spartan-3E FPGA Starter Kit Board page http://www.xilinx.com/s3estarter

- UG230: Spartan-3E FPGA Starter Kit User Guide

### Introduction

As described in Architectural Overview, the Spartan-3E FPGA architecture consists of five fundamental functional elements:

- Input/Output Blocks (IOBs)

- Configurable Logic Block (CLB) and Slice Resources

- Block RAM

- Dedicated Multipliers

- Digital Clock Managers (DCMs)

The following sections provide detailed information on each of these functions. In addition, this section also describes the following functions:

- Clocking Infrastructure

- Interconnect

- Configuration

- Powering Spartan-3E FPGAs

### Input/Output Blocks (IOBs)

For additional information, refer to the "Using I/O Resources" chapter in <u>UG331</u>.

### **IOB** Overview

The Input/Output Block (IOB) provides a programmable, unidirectional or bidirectional interface between a package pin and the FPGA's internal logic. The IOB is similar to that of the Spartan-3 family with the following differences:

- Input-only blocks are added

- Programmable input delays are added to all blocks

- DDR flip-flops can be shared between adjacent IOBs

The unidirectional input-only block has a subset of the full IOB capabilities. Thus there are no connections or logic for an output path. The following paragraphs assume that any reference to output functionality does not apply to the input-only blocks. The number of input-only blocks varies with device size, but is never more than 25% of the total IOB count.

Figure 5 is a simplified diagram of the IOB's internal structure. There are three main signal paths within the IOB: the output path, input path, and 3-state path. Each path has its own pair of storage elements that can act as either registers or latches. For more information, see Storage Element Functions. The three main signal paths are as follows:

• The input path carries data from the pad, which is bonded to a package pin, through an optional programmable delay element directly to the I line. After the delay element, there are alternate routes through a pair of storage elements to the IQ1 and IQ2 lines. The IOB outputs I, IQ1, and IQ2 lead to the FPGA's internal logic. The delay element can be set to ensure a hold time of zero (see Input Delay Functions).

- The output path, starting with the O1 and O2 lines, carries data from the FPGA's internal logic through a multiplexer and then a three-state driver to the IOB pad. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- The 3-state path determines when the output driver is high impedance. The T1 and T2 lines carry data from the FPGA's internal logic through a multiplexer to the output driver. In addition to this direct path, the multiplexer provides the option to insert a pair of storage elements.

- All signal paths entering the IOB, including those associated with the storage elements, have an inverter option. Any inverter placed on these paths is automatically absorbed into the IOB.